1. 引言

电子具备电荷和自旋这两大固有属性,但传统的cmos器件技术还是主要依赖于电子电荷来描述和处理相关信息。受到电子引发的隧道效应、功率损耗和传输延迟等多重因素的影响,这些技术正逐步接近其在物理方面的极限状态。在最近几年中,人们逐渐开始研究如何通过调整电子的运动状态来对信号或能量进行有效调控。与传统的cmos器件技术相比,自旋电子器件主要利用电子自旋来表示信息,且具有几个显著的优点:首先,它们利用电子隧穿来产生自旋电流,而不是通过抑制电子隧穿来产生自旋电流。当cmos器件的特性尺寸进一步缩小时,自旋电子器件将不再需要面对物理尺寸极限的挑战;第二,自旋电子器件通常具有零静态功耗和极低动态功耗的优点,这使得功耗问题得到了有效的缓解;第三点是,自旋电子器件能够与电路直接连接,这解决了在设计过程中需要考虑的电路设计、制造工艺以及封装流程等多个复杂问题;第四点是,自旋电子器件通常利用纳磁体的磁矩来存储数据,通过输入接口电路传输信息,这种非易失性有助于采纳cmos器件难以应用的内部存储逻辑结构,从而规避了全局互连的问题,并进一步解决了全局互连延迟的难题。如前所述,这些优点预示自旋电子器件有潜力成为未来电子设备的核心选择 [1] [2] [3] 。

在自旋电子学的研究中,如何达到高效且低能耗的操作方式一直是众多研究者关注的焦点。自旋电子器件以其低功耗、高集成度和低成本的优势得到越来越多研究者的关注与青睐,并取得一系列重要研究进展。迄今为止,已经提出了大量具有创新性的自旋电子器件,这些器件包括纳磁逻辑 [4] 、自旋场效应晶体管 [5] 、自旋波器件 [6] 、磁畴壁逻辑器件 [7] 以及全自旋逻辑器件(all spin logic device asld) [8] 等。这些新型自旋电子器件具有低功耗、高效率、低成本和易于集成等优点,为自旋电子学技术带来新的挑战与机遇。在这其中,以磁性半导体材料为基础的自旋电子学成为了研究焦点,其进展主要聚焦于如何成功实施自旋电子开关和如何搭建高效的自旋电子学器件。

需要特别强调的是,asld由于其在自旋信息和电荷信息转换过程中无需额外的硬件设置,因此具有结构简洁、能量消耗极低以及非易失性等优点,这一点吸引了众多学者的研究兴趣。因此,基于全自旋逻辑器件构建更为完善的电路逻辑网络成为全自旋逻辑电路发展的方向之一。目前,基于全自旋逻辑器件的电路结构设计研究还相对较少,已知的电路结构主要包括反相器、择多逻辑门、全加器、rs触发器、d触发器、数值比较器、译码器、编码器等 [8] - [14] ,但作为数字逻辑电路中的一个重要组成部分——奇偶校验器还未见报道。因此,本文设计了一种基于全自旋逻辑器件的三输入奇偶校验器,这对于基于asld器件构建更完整的逻辑电路具有重要的意义。

2. 基于asld的三输入奇偶校验器设计

2.1. 电路原理

全自旋逻辑(all spin logic, asl)电路与传统的cmos电路不同,基本逻辑门不再是与非门,而是反相器和择少/择多逻辑门。对于择少逻辑门来说,当输入中0占多数时,输出为1,当1占多数时,输出为0;而对于择多逻辑门,结果正好相反。因此,为了避免输入中0和1占比恰好相等进而导致输出错误的情况,择少/择多逻辑门的输入个数通常是奇数个。一般来说,可以实现3输入、5输入、7输入等择少/择多逻辑门,可用m3 ()、m5 (

)、m7 (

)来表示,这里通过统一使用五输入择少逻辑门与七输入择少逻辑门,可对三输入奇偶校验器进行更好的时钟控制。

对于五输入择少逻辑门,其逻辑表达式为:

(1)

其中五输入择少逻辑门的两个输入端d和e置1时,可实现三输入或非操作,其逻辑表达式为:

(2)

同样地,对于七输入择少逻辑门,若将其三个输入端e,f与g置1时,可实现四输入或非操作,其逻辑表达式为:

(3)

图1为基于全自旋逻辑器件的三输入奇偶校验器平面示意图,其中gate1到gate4是五输入择少逻辑门,gate5是七输入择少逻辑门,gate6是反相器。另外,箭头表示磁体的磁矩方向,其中双向箭头表示磁矩方向待定,单向箭头表示磁矩方向确定,用指向−x轴方向表示逻辑0,指向 x轴方向表示逻辑1,根据图1所示平面电路图可更直观了解三输入奇偶校验器的公式推理及输出过程。

利用五输入择少逻辑门,七输入择少逻辑门和反相器,可以得到三输入奇偶校验器的两个输出端的逻辑表达式为:

(4)

(5)

另外,由式(4)、(5)可得其真值表如表1所示。

由表1可看出,在a,b,c中1的个数为奇数时,输出y为1;在a,b,c中1的个数为偶数时,输出z为1。

. three-input parity checker truth table

表1. 三输入奇偶校验器真值表

. three-input parity checker planar schematic based on full spin logic device

图1. 基于全自旋逻辑器件的三输入奇偶校验器平面示意图

2.2. 电路实现及工作原理

在asl电路设计中,信息的表示并不是基于电压的高低,而是通过磁体的磁矩方向来进行的。因此,在驱动电路运行的过程中,除了需要输入电压信号外,还必须为磁体设定一个初始的磁矩方向。我们采用输入接口电路为电路供应输入信号,并在下面对其各自的功能做了详细描述。

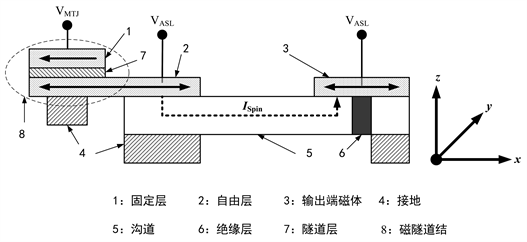

输入接口电路如图2所示,其中磁隧道结(magnetic tunnel junction, mtj)的固定层磁矩保持不变,而mtj的自由层作为asl器件的输入端,通过在改变加在mtj上电压vmtj的极性可改变自由层的磁矩方向,进而实现对asl器件输入逻辑0或逻辑1。

为了确保输入接口电路的正常运行,需要让mtj上的电压vmtj与asl上的电压vasl各自独立工作。首先,在mtj的两侧施加电压vmtj,此时的vasl等于0 v。在vmtj电压为正电压的情况下,自由层的磁矩与固定层是相反的;但在vmtj电压为负电压的情况下,自由层的磁矩与固定层保持一致。在完成自由层磁矩的写入后,将vmtj设置为0 v。此时,在自由层和输出端的磁体上都会添加电压源vasl。当电压源vasl为正电压时,输出端的磁矩与自由层是相反的;而当电压源vasl为负电压时,输出端的磁矩与自由层保持一致,从而实现了从自由层到输出端的信号传输。

. asl device with input interface

图2. 带输入接口的asl器件

五输入择少逻辑门是实现逻辑运算的核心器件,其平面示意图如图3所示。

. schematic diagram of a five-input selective logic gate plane

图3. 五输入择少逻辑门平面示意图

图3中,in1~in5分别表示5个输入端,out1表示输出端。白色箭头表示磁矩方向,其中双向箭头表示磁矩方向待定,单向箭头表示磁矩方向固定。要注意的是,输入端in1、in2和in3分别通过输入接口与c、b和a相连,其磁矩方向由加在mtj上的电流方向和mtj固定层磁矩方向共同决定。而输入端in4和in5的磁矩方向指向 x轴方向,表示输入逻辑1。通过在磁体上加上正的工作电压,上述结构可实现式(2)所示五输入择少逻辑功能。

七输入择少逻辑门的平面示意图如图4所示。

. schematic diagram of a seven-input selective logic gate plane

图4. 七输入择少逻辑门平面示意图

在图4里,in1至in7代表6个输入端,而out2则代表输出端。输入端的in5、in6和in7的磁矩方向是 x轴方向,这代表了输入逻辑1。通过在磁体上施加正向的工作电压,可以实现上述结构所示的七输入择少逻辑功能。

图5展示了一个基于asl器件的三输入奇偶校验器的三维结构图。磁体层一般是由具有水平方向异质性的铁磁材料构成的,例如镍、钴以及坡莫合金 [15] 。沟道层通常由具有较长自旋扩散长度的金属或半导体组成,例如铜、铝、银、硅和石墨烯 [16] [17] [18] [19] 。通常,接地层是由电阻率相对较低的金属元素,例如铜和银,组成的。为了保证信号在传输过程中不会出现倒易性,隔离层被精心设计成了一层绝缘材料 [9] 。

从图6展示的逻辑电路图中,我们可以观察到,为了实现三输入奇偶校验器,不仅需要原始变量,还需要反变量。通常的方法是利用反相器来处理原始变量。在本文中,我们通过比较输入接口中mtj固定层的磁矩方向来实现原始变量和反变量的输入,从而避免了使用额外的反相器,极大地简化了电路的结构。具体的操作方式是,如果输入信号呈现为原始变量,那么输入接口的固定层的磁矩会指向-x轴;而如果输入信号呈现为反变量,那么输入接口的固定层磁矩则会指向 x轴。

从整体和平面的电路图中,我们可以观察到三输入奇偶校验器是由4个五输入择少逻辑门、1个七输入择少逻辑门以及1个反相器组成的。在gate1中,a、b、c都是以原始变量的方式呈现,因此连接在a、b、c端的mtj固定层的磁矩都是朝向−x轴的方向。对于gate2,a是以原始变量的方式呈现,而b、c则是以反变量的方式呈现。因此,与a端连接的mtj固定层的磁矩是朝向−x轴的方向,而与b和c端连接的mtj固定层的磁矩则是朝向 x轴的方向。在gate3中,b是以原始变量的方式呈现,而a和c则是以反变量的方式呈现。因此,与b端连接的mtj固定层的磁矩是朝向−x轴的方向,而与a和c端连接的mtj固定层的磁矩则是朝向 x轴的方向。在gate4中,c以原始变量的方式呈现,而a和b则以反变量的方式呈现。因此,与c端连接的mtj固定层的磁矩是朝向−x轴的方向,而与a和b端连接的mtj固定层的磁矩则是朝向 x轴的方向。另外,在gate1至gate4的输入端,in4和in5均为输入1,这意味着磁体的磁矩都是固定在 x轴的方向上。

此外,从gate1到gate4的输出端分别作为gate5的四个输入端in1~in4,而其他三个输入端in5、in6和in7都是输入1,因此它们的磁体磁矩都是固定指向 x轴方向的。

从公式中我们可以得知,偶校验位z实际上是奇校验位y的逆变量,我们可以使用反相器gate6来从y中反推出z。

. overall layout of a three-input parity checker based on an all-spin logic device

图5. 基于全自旋逻辑器件的三输入奇偶校验器整体布局图

. three-input parity checker circuit schematic

图6. 三输入奇偶校验器电路原理图

3. 基于asld的三输入奇偶校验器的时钟控制流程

mtj自由层磁矩的转换时间以及asl器件信号传输延迟时间一般为纳秒级。mtj的工作电压一般小于1 v,而asl的工作电压一般为毫伏级。因此,为说明问题的方便,后面我们假设每种信号的持续时间为2 ns,加在mtj上的电压幅度为0.1 v,加在asl器件上的电压幅度为10 mv。

要让奇偶校验器能正常工作,还需要给电路加上适当的控制信号,其输入信号和工作电压先后顺序如图7所示。控制方案具体如下:

在0~2 ns期间,在a、b、c端根据输入信号加载电压,如果输入逻辑0,则其电压为−0.1 v,如果输入逻辑1,则电压为0.1 v。(有必要说明的是,在0~2 ns期间,a、b、c端上电压的高低共有8种组合情况,代表着奇偶校验器3个输入端的8种输入情况,本图用虚线表示输入可能是−0.1 v和0.1 v两种不同的情况)。同时,加在asl上的工作电压vclk1到vclk4都为零,择少逻辑门和反相器都不工作。

在2~4 ns期间,已完成了信号的输入,让a、b、c端上的电压为0 v,使得mtj自由层磁矩方向保持不变。而时钟信号vclk1、vclk2的电压变为10 mv,此时gate1~ gate4开始工作,实现五输入择少逻辑功能,而时钟信号vclk3到vclk4为零,gate5和gate6不工作。

在4~6 ns期间,a、b、c端上的电压依然保持为0 v,而时钟信号vclk2和vclk3的电压设置为10 mv,时钟信号vclk1、vclk4为零,此时gate1~ gate4和gate6不工作,gate5开始工作,实现了奇校验的输出。

在6~8 ns期间,a、b、c端上的电压依然保持为0 v,时钟信号vclk1和vclk2为零,此时gate1~ gate5不工作,而时钟信号vclk3和vclk4的电压设置为10 mv,此时gate6开始工作,实现了偶校验的输出。

. input signal and operating voltage waveform

图7. 输入信号和工作电压波形图

4. 总结

本文首先基于全自旋逻辑器件构建了三输入奇偶校验器,与传统的cmos器件技术构造的奇偶校验器相比,基于asld的三输入奇偶校验器采用了磁隧道结来为电路提供输入信号,通过利用磁隧道结固定层磁矩指向的不同来实现原变量和反变量的输入,避免了额外使用反相器,同时利用了五输入择少逻辑门,七输入择少逻辑门和反相器,极大地减小的电路的结构。其次,说明了利用五输入择少逻辑门,七输入择少逻辑门和反相器构造的三输入奇偶校验器的电路原理,并介绍了asl器件的工作原理与五输入择少逻辑门,七输入择少逻辑门的工作过程。最后,提出了一种时钟控制方法,在每个时钟周期为2 ns时,利用四个时钟周期和电压控制,实现了三输入奇偶校验器的奇偶校验输出。利用asld的超高集成度、超低功耗、抗辐射和非易失等优点,有望在未来设计更大规模,更复杂的全自旋逻辑电路。